We choose to do these things "not because they are easy, but because they are hard".

Weekly Report, 2023-08-02

#### Hall A - ECal

Brian Eng, Mindy Leffel, and Marc McMullen

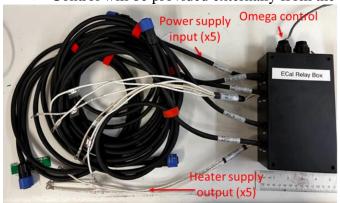

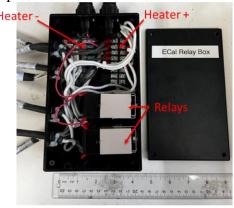

- Designed, fabricated, and tested over-temperature relay box

- **★** Control will be provided externally from the Omega process controller

- Continued modifying controls software

- ★ All five control zones read back temperature and send the appropriate control value to the controls shared variable

- Fabricated one high voltage cable with Fischer connectors; 10/23 completed

#### **Hall B - Central Calorimeter**

Mindy Leffel

• Tested and labeled 24 LEMO and 28 SHV cables

#### Hall B - Gas System

Brian Eng

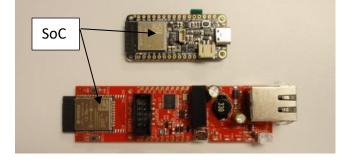

- Swapped to microcontroller with Power-over-Ethernet instead of WiFi for network access

- **★** Uses same family of SoC (System on a Chip) and also runs Arduino, so only minimal code changes needed

Top (black) = previous board, bottom (red) = new board

We choose to do these things "not because they are easy, but because they are hard".

Weekly Report, 2023-08-02

#### Hall C - NPS

Mary Ann Antonioli, Peter Bonneau, Aaron Brown, Pablo Campero, Brian Eng, Mindy Leffel, and Marc McMullen

- Debugging thermal readback and chiller controls LabVIEW program

- \* After the LabVIEW program is stopped and restarted, the chillers do not read back the correct value for the temperature setpoint—default value is 20°C, but are reading 634.4°C

- LabVIEW code is written so that the chillers cannot be turned on if the setpoint and the readback setpoint do not match

- To recover, temperature setpoint must be changed to a value other than 20°C until the chiller reads back the correct value

- Contacted company; awaiting reply

- Troubleshooting random failure of *create subVI* option in LabVIEW menu

- **★** NI suggests copying folder or reinstalling software; can work around issue, but takes more steps to create subVI

- Creating subVIs from array loops; completed trip delay enable break-out and hi limit break-out

- Worked with Ansys technical support on why the steady state and transient simulations didn't match; there were two causes

- ★ When the geometry of the steady state simulation was copied to the transient simulation, material assignments did not get copied—all model components were assigned the default of structural steel

- **★** The applied heat load of 0.3 W was done as heat flux instead of heat flow

- Ran simulations for 0°C, 1°C, 5°C, and 10°C increases in ambient temperature

- \* Results confirm that the temperature of the crystals is dictated by the ambient temperature

We choose to do these things "not because they are easy, but because they are hard".

Weekly Report, 2023-08-02

- Debugging surface mesh and volume mesh of module for thermal analysis due to errors received when trying to perform the volume mesh

- **★** Checking minimum and maximum size of mesh cell elements for faces

- **★** Checking local sizing options for conflicting sections and parts

- **★** Checking minimum and maximum size of mesh cell elements for volumes

- Made Visio drawing of Phoebus alarm test station simulator

- Completed integrating alarm system with signal simulator

- **★** Signal simulator generates EPICS PVs

- **★** Phoebus alarm system server programmed to monitor simulator PVs

- **★** Test of alarm system monitoring of PVs in progress

#### Hall D - JEF

### Mindy Leffel

• Populated 40 PMT bases; 485 of 1200 completed

#### **EIC**

### Brian Eng

- Presented latest results with multi-layer insulation

- **★** Suggestion made to try additional layers

- ★ Concerns about how to get higher flow into the detector versus the four, ½" lines being used in the test stand

We choose to do these things "not because they are easy, but because they are hard".

Weekly Report, 2023-08-02

#### **EIC - DIRC**

Mindy Leffel, Tyler Lemon, and Marc McMullen

- Testing and debugging laser interlock system PCB

- ★ Solid state relay inputs were drawing too much current, causing them to fail closed; 24 V output remained enabled even when an interlock was present

- Solved by adding resistors to relay inputs to lower current drawn by component

- **★** Some inputs were floating high, causing inputs to ICs to always be true

- Solved by adding pull-down resistors to any input floating high

- Began Visio flowcharts of DIRC user interface; completed main program and serial connect sub-routine

- Ordered additional relays for the interlock system PCB

- Developing Phoebus alarm system test

- \* Researched and procured readout hardware for test

#### **EIC - Thermal Test Stand**

Pablo Campero, Brian Eng, George Jacobs, and Marc McMullen

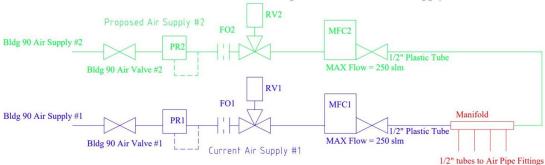

• Created drawing with second air supply

EIC Thermal Test Stand Proposed Addition of Air Supply #2

• Discussed additional compressed air line with the pressure systems design authority